Архитектура mips что это

Сегодня MIPS стал Open Source, против RISC-V и ARM. Как Россия повлияла на стратегию американской процессорной компании

То, о чем говорили сторонники Open Source с 1980-х — свершилось! Сегодня архитектура процессоров MIPS стала Open Source. Учитывая, что такие компании как Broadcom, Cavium, китайский ICT и Ingenic платили MIPS за архитектурную лицензию (право сделать совместимую по системе команд микроархитектурную реализацию) миллионы долларов (иногда более десяти миллионов), это историческая веха. Теперь у RISC-V нет преимущества в этом аспекте, да и ARM придется оправдываться. У MIPS до сих пор есть технические преимущества перед RISC-V — лучшая плотность кода у nanoMIPS, лучшая поддержка аппаратной многопоточности, лучшие бенчмарки на high-end ядрах, более полная экосистема. И 8 миллиардов выпущенных чипов на основе MIPS.

Вот команда разработчиков 64-битного процессорного ядра MIPS I6400 «Samurai» и MIPS I6500 «Daimyo» в Сан-Франциско. Это ядро лицензировала в частности японская компания автомобильной электроники DENSO, поставщик Тойоты:

А вот представители российской компании ЭЛВИС-НеоТек вместе с русскими, украинскими и казахстанским разработчиком ядер MIPS и софтвера для него. ЭЛВИС-НеоТек является как лицензиатом ядер MIPS, так и разработчиком собственного по микроархитектуре ядра, совместимого с архитектурой MIPS. А также аппаратных блоков видео-обработки и алгоритмов распознавания:

Российское MIPS-коммьюнити оказано непосредственное влияние на этот шаг:

Сегодня я разговаривал с президентом MIPS Артом Свифтом. До нынешнего поста Арт был вице-председателем комитета по маркетингу RISC-V, вице-президентом Sun, DEC и Cirrus Logic. Я спросил у Арта, чем же отличается Open MIPS от не ставшего популярным Open SPARC.

Арт ответил, что Sun Microsystems была открытой только на словах и не очень любила строить коммьюнити. А вот мы в Open MIPS будем заниматься именно построением коммьюнити. Причем методы построения всемирного коммьюнити будут основаны на опыте строительства MIPS-коммьюнити в России (!), а точнее на работе с российскими компаниями (ЭЛВИС-НеоТек, Байкал Электроникс, НИИСИ, НИИМА Прогресс) и университетами, которые проводили семинары по MIPSfpga (МИЭТ, МФТИ, ИТМО, МИФИ, МГУ, СГАУ, НГТУ, ТГУ, КПИ и другие).

Немного истории. Истоки MIPS — в Стенфорде начала 1980-х годов. В 1984 году была основана компания MIPS Computer Systems, которая потом неоднократно меняла владельцев (Silicon Graphics, MIPS Technologies, Imagination Technologies, Wave Computing). В том же 1984 году возникла и компания ARM. Вот основатель MIPS Джон Хеннесси с первым чипом:

Впоследствие MIPS использовался в ранних игровых приставках Nintendo64 и Sony Playstation. Вот девушка Ирина в музее компьютеров рядом с рабочими станциями Silicon Graphics, которые использовались для съемок первых реалистично-графических голливудских фильмов, включая «Парк Юрского Периода». Эти же компьютеры упомянуты в романе русского писателя Виктора Пелевина «Поколение П». Внутри — процессор MIPS R4000:

А вот — встреча в прошлом году в Москве участников семинаров по MIPSfpga, образовательной программы, в которой университетские исследователи могут модицифировать реальный промышленный процессор MIPS interAptiv UP, синтезировать его для ПЛИС и посмотреть, как он работает, в том числе в потактовом режиме. В центре — Роберт Оуэн, менеджер образовательных программ Imagination Technologies, слева от него — Станислав Жельнио, автор российского учебного ядра schoolMIPS (его можно найти на GitHub):

В вот российский компьютер на основе процессора КОМДИВ-64, с вариантом архитектуры MIPS + спроектированной в России микроархитектурой + разработанными в России векторными расширениями архитектуры:

А вот Максим Горбунов, менеджер из НИИСИ, где был спроектирован КОМДИВ-64. Максим — второй слева, между специалистом по образовательным программам из российского Самсунга Татьяной Волковой и специалистом по образованию школьников из МФТИ Андреем Огневым:

Вот в офисе лицензиата MIPS Байкал Электроникс. Процессор Байкал-Т1 на основе MIPS P5600 «Apache» используется сейчас в российских контроллерах станков и сетевых устройствах:

А вот в Киевском Политехническом Институте на хакатоне MIPSfpga. Победители этого хакатона впоследствие получили бронзу на европейском финале конкурса Innovate FPGA, организованного Интелом:

Этот хакатон также вошел в презентации и статьи про практику MIPSfpga в университетах:

MIPS вдохновил создателей специализированных вычислительных устройств, например David Wentzlaff, который читает курс по продвинутой процессорной архитектуре в Принстоне и на Курсере:

Устройство, которое разработано Девидом, предстваляло из себя сетку (mesh) из 64 процессоров. Интересно, что сейчас Wave Computing, компания, частью которой является MIPS, тоже работает над сеткой, но из десятков тысяч процессорных элементов. Эта архитектура предназначена для ускорителя нейросетей, чипа на 7 нанометров, который Wave Computing разрабатывает совместно с Broadcom. Вот в офисе Wave Computing в Campbell, California. Слева специалист по функциональной верификации и UVM Jon Wang, а справа старший директором по Custom Design Steve Dilbeck. Стив — большой авторитет в asynchronous design, dynamic logic и разных эффектах на уровне транзисторов, когда размеры опускаются до 7 нанометров, а частоты поднимаются выше 6 гигагерц:

Вот слайд из презентации по нейроускорителю:

Изучаем MIPS-ассемблер

Как говорит Википедия, MIPS – микропроцессор, разработанный компанией MIPS Computer Systems (в настоящее время MIPS Technologies) и впервые реализованный 1985 году. Существует большое количество модификаций этой архитектуры, созданных специально для 3D-моделирования, быстрой обработки чисел с плавающей запятой, многопотоковых вычислений. Различные варианты этих процессоров использутся в роутерах Cisco и Mikrotik, смартфонах, планшетах и игровых консолях.

Инструкции MIPS достаточно просты для понимания, и именно с него рекомендуется начинать изучение ассемблера. Чем сейчас, собственно, и займёмся.

Структура программы на MIPS-ассемблере

Типы в MIPS-ассемблере

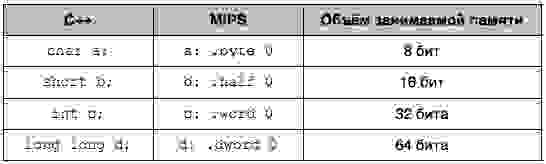

Вот сравнительная таблица основных типов в C++ и в MIPS:

Как можно увидеть в таблице, выбор типа в для переменной в MIPS основывается только на объёме памяти, который будет занимать эта переменная. Обратите внимание, что MIPS в этом плане не различает signed- и unsigned-переменные.

Метки (символы)

Основные директивы

Немного глубже мы рассмотрим типы данных по мере их использования в коде.

Регистры

Инструкции MIPS

Примечание. C этого момента мы будем рассматривать MIPS-процессор, его инструкции и дополнения на примере замечательного симулятора MIPS под названием MARS, который можно загрузить отсюда. Имплементация MIPS в этом симуляторе полностью соответствует стандартам.

В коде в начале статьи мы уже выделили все функциональные части программы и определили инструкции и псевдоинструкции как то, что не является комментарием, символом (меткой) или директивой. Псевдоинструкции также называют макросами, они трансформируются в одну или несколько инструкций во время выполнения кода. Вот пример макроса:

переходит в набор инструкций:

Как видно, MIPS-программы всегда записываются по одной инструкции на строчку.

Типы инструкций

Также существуют инструкции для сопроцессоров, но их мы рассмотрим позже.

Инструкция syscall

Весь ввод и вывод происходит через консоль MARS’a.

Арифметические инструкции

Кстати, imm16 по умолчанию интерпретируются как позитивные. Например:

Если нужно добавить отрицательное значение, то нужно явно это указать:

А теперь можно протестировать получившийся код в MARS. Загрузите черновик вот отсюда и откройте его в MARS:

Продолжение следует

В следующей статье рассмотрим логические инструкции, а также умножение и деление целых чисел. В ней же попробуем работать с памятью и стеком. А пока предлагаю вам попробовать переписать вот этот код на MIPS-ассемблер:

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

MIPS (Microprocessor without Interlocked Pipeline Stages)

| Дизайнер | MIPS Technologies |

|---|---|

| Биты | 64-bit (32→64) |

| Представлен | 1981 |

| Дизайн | RISC |

| Тип | Регистр-регистр |

| Кодирование | фиксированное |

| Разветвление | по сравнению двух регистров |

| Порядок байтов | Bi-endian (big→bi) |

| Расширения | MDMX, MIPS-3D, MIPS16e, MIPS MT |

| Регистры | |

| FPU (Floating Point Unit) | 32 (для double используются пары регистров в 32-битных версиях процессора) |

Содержание

Описание

Семейство ядер MIPS идеально для устройств, где необходимо сверхнизкое энергопотребление и каждая единица площади на счету. Семейства MISC процессоров удовлетворяют любым нуждам: от любителей, до профессионалов. MISC процессоры умеют выполнять такие задачи, как многоядерность на уровне железа, совместимая с 32/64-битными инструкциями в множестве архитектур ISA, а так же предоставить стабильность работы, недостижимую аналогичным устройствам в той же ценовой категории.

Архитектура

Основа сегодняшних процессоров MIPS была заложена в первой половине 1980х. Основой являлся 32-битная RISC процессор, задачей которого было предоставление самых высоких уровней производительности вместе с новыми недостижимыми возможностями эффективности, которые стали достижимыми, благодаря архитектуре, не имеющей лишних и ненужных деталей. Процессоры MIPS предоставляют низкое потребление и меньший размер относительно своих конкурентов, благодаря огромному опыту, накопленному за несколько десятилетий. Процессоры используются в огромном множестве устройств, от роутеров до телевизоров.

MIPS состоит из широкого множества энергоэффективных, высокопроизводительных встраиваемых микропроцессорных ядер, которые управляют миллиардами продуктов. Эти процессоры идеальны для будущих поколений встраиваемых архитектур на множестве быстрорастущих рынков, включая цифровое потребление, мобильный рынок, широкополосный доступ в интернет, сети и множество других. Чтобы удовлетворить требованиям всех рынков, кастомизируемые процессоры MIPS варьируются от самых простых до наиболее высокопроизводительных.

Aptiv-процессорные ядра

microAptiv™

Высокоэффективные, компактные встраиваемые процессорные ядра с функциональностью microMIPS включают в себя DSP и SIMD функциональность, чтобы обрабатывать сигналы, требуемые широкому множеству микроконтроллеров и встраиваемым системам начального уровня, включая автоматизированные системы управления, интеллектуальные счетчики, автомобильные, проводные / беспроводные системы коммуникации.

interAptiv™

Процессорное ядро использует сбалансированный девятиступенчатый конвейер с поддержкой мультипоточности и является высокоэффективным среди конкурентов. Идеально для распараллеливаемых приложений, требующих оптимизаций энергопотребления, таких как шлюзы связи, устройства приема LTE сигнала, контроллеры SSD дисков и автомобильное оборудование.

proAptiv™

Процессор с архитектурой вычислительного ядра, которая использует несколько декодеров команды, которые умеют загружать работой множество исполнительных блоков. Планирование исполнения потока команд является динамическим и осуществляется самим вычислительным ядром. Среди всех лицензируемых ядер, достигает наибольших частот, вместе с высокой энергоэффективностью. Подходит для ресурсозатратных приложений.

Ядра MIPS Series5 Warrior

Продукты

Версии множества инструкций MIPS

MIPS I

MIPS II

MIPS Computer Systems R6000 микропроцессор, представленный в 1989 году, является первой реализацией MIPS II. Предназначен для серверов, R6000 был изготовлен и продан Bipolar Integrated Technology, но был коммерческим провалом. В середине 1990-х годов многие новые 32-разрядные процессоры MIPS для встраиваемых систем были реализациями MIPS II, так как введение в 1991 году 64-разрядной архитектуры MIPS III сделало MIPS II самой новой 32-разрядной архитектурой MIPS, пока в 1999 году не была введена MIPS32.

MIPS III

MIPS Computer Systems R4000 микропроцессор, представленный в 1991 году, была первой реализации MIPS III. Он был разработан для использования на персональных компьютерах, компьютерах рабочих станций и серверах. MIPS Computer Systems активно продвигали архитектуру MIPS и R4000, создавая консорциум Advanced Computing Environment (ACE) для продвижения своего стандарта Advanced RISC Computing (ARC), целью которого было установить MIPS в качестве доминирующей платформы персональных компьютеров. ARC не добился большого успеха в персональных компьютерах, но R4000 (и производная от R4400) широко использовались на рабочих станциях и серверных компьютерах, особенно его крупнейшим пользователем, Silicon Graphics. Другое использование R4000 включало высококачественные встроенные системы и суперкомпьютеры. MIPS III был в конечном итоге реализован рядом встроенных микропроцессоров.

MIPS IV

MIPS IV — четвёртое поколение архитектуры, представляет собой расширенную версию MIPS III и совместим со всеми существующими моделями MIPS. Первая реализация MIPS IV была представлена в 1994 году под названием R8000. MIPS IV включил в себя:

MIPS V

MIPS V — пятая версия архитектуры, была представлена 21 октября 1996 года на Микропроцессорном форуме 1996 года. Эта модель была разработана для того, чтобы повысить производительность графических 3D-приложений. В середине 1990-х большая часть не встроенных микропроцессоров MIPS приходилась на графические терминалы от SGI. Разработка MIPS V была дополнена целочисленными мультимедийными расширениями MDMX (MIPS Digital Media Extensions), которые были представлены в тот же день, что и MIPS V.

Реализации MIPS V так никогда и не были внедрены. В 1997 году SGI представила микропроцессоры под названиями «H1» («Beast») и «H2» («Capitan»), которые должны были быть произведены в 1999 году. Но вскоре их объединили, и в конечном итоге в 1998 году эти проекты были отменены.

В MIPS V был добавлен новый тип данных — PS (pair-single), который представляет собой два числа с плавающей запятой двойной точности (32-битные), хранящиеся в 64-битном регистре с плавающей запятой. Чтобы работать с этим типом данных в режиме SIMD, были добавлены различные варианты арифметических, сравнительных операций над числами с плавающей запятой, а также команда условного перехода. Появились новые инструкции для загрузки, реконфигурации и преобразования PS-данных. Это первая архитектура, сумевшая реализовать обработку чисел с плавающей запятой в SIMD-режиме с имеющимися ресурсами. [Источник 1]

MIPS32/MIPS64

Множества 32-битных инструкций MIPS32 и 64-битных инструкций MIPS64 были представлены в 1999 году. MIPS32 основан на MIPS II с некоторыми дополнительными функциями от MIPS III, MIPS IV, MIPS V; MIPS64 основан на MIPS V. Такие корпорации как NEC, Toshiba, SiByte приобрели лицензии на множество инструкций MIPS64 сразу после их анонса. Остальные корпорации, такие как Philips, присоединились к ним позже.

MIPS32/MIPS64 релиз 1

Первая версия MIPS32, основанная на множестве инструкция MIPS II добавила перемещения по условиям, инструкции перемещения и другие возможности из семейств R4000 и R5000 64-битных процессоров. Первая версия MIPS64 добавила режим выполнения запуская 32-битного когда.

MIPS32/MIPS64 релиз 2

MIPS32/MIPS64 релиз 3

MIPS32/MIPS64 релиз 4 (пропущен)

Пропущен, так как с числом 4 в некоторых азиатских странах связанно дурное поверье.

MIPS32/MIPS64 релиз 5

Анонсирована в 2012.

MIPS32/MIPS64 релиз 6

MIPS32/MIPS64 2014 года добавляла следующие возможности:

Удалены редко используемые инструкции:

Изменилась кодировка команд, освободилось место для будущих расширений. [Источник 2]

Расширения на уровне приложений

MIPS MCU ASE

Улучшения для приложений микроконтроллеров. Разработан для расширения прерывания поддержки контроллера, уменьшения задержки и улучшений контроля ввода вывода типичных для микроконтроллерных систем.

MIPS16

MIPS16e

MIPS16e2

MIPS DSP ASE

DSP ASE является дополнительным расширением для MIPS32 / MIPS64 Release 2 и более новых наборов команд, которые можно использовать для ускорения большого диапазона вычислений «мультимедиа», в частности аудио и видео. Модуль DSP содержит набор инструкций и состояний в целочисленном конвейере и требует минимальной дополнительной логики для реализации в ядрах процессора MIPS. Редакция 2 ASE была представлена во второй половине 2006 года. Эта ревизия добавляет дополнительные инструкции к оригинальной ASE, но в остальном обратно совместима с ней. В отличие от основной части архитектуры MIPS, это довольно нерегулярный набор операций, многие из которых выбраны для определенной релевантности некоторому ключевому алгоритму. [Источник 3]

MIPS SIMD

Множество расширений инструкций предназначены для ускорения мультимедиа.

eXtended Physical Address (XPA)

Расширяет до 40 бит физический адрес (до 1 ТБ).

MIPS Virtualization

Поддержка на уровне железа технологий виртуализации

MIPS Multi-Threading

MIPS или ARM?

От выбора архитектуры процессора зависит производительность, а также время разработки и стоимость устройства. В статье подробно описана архитектура MIPS32 ядер М4К и М14К. Сравнение архитектур MIPS32 и Cortex-M показывает преимущества первой.

Архитектура MIPS

Архитектура MIPS впервые была применена в процессоре R2000 в 1985 г. C тех пор она претерпела ряд изменений и сейчас изготавливается в двух вариантах: 32- и 64-рарядном, MIPS32 и MIPS64, соответственно.

В основе MIPS лежит гарвардская архитектура и набор команд RISC. Конвейер содержит 5 уровней (см. рис. 1) и логические схемы, обеспечивающие еще до завершения обработки инструкции быстрый доступ к данным, которые используются следующей инструкцией. Все арифметические и сдвиговые операции выполняются за один цикл. Для ускорения отдельных процессов предусмотрены опциональные специализированные расширения, в число которых входят MIPS16e, SmartMIPS, блок многопотоковых вычислений и модули обработки сигнала и объемного изображения.